5.4 Коди з виявленням помилок

До найбільш поширених кодів з виявленням помилок відносять код з перевіркою на парність, коди з прямим та інверсним повторенням та кореляційний код. Розглянемо їх детальніше.

5.4.1 Код із перевіркою на парність

Код містить лише один надлишковий символ. Вибирається надлишковий символ таким чином, щоб загальна кількість одиниць у кодовій комбінації була парною. Перевірка кодової комбінації робиться шляхом підсумовування за модулем два всіх його символів. Надмірність коду дорівнює

,

,

де n – довжина кодової комбінації;

r = 1 – число перевірних символів.

Код дозволяє виявляти однократні помилки і всі помилки непарної кратності, тому що тільки в цих випадках кількість одиниць у комбінації стане непарною. Не виявляються помилки парної кратності.

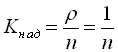

Кодер коду з перевіркою на парність

Кодером коду з перевіркою на парність є електронний пристрій, який при надходженні на його входи п інформаційних символів двійкового коду автоматично добавляє до iнфopмaцiйниx символів один контрольний символ «0» чи «1», значення якого залежить від клькості одиниць в двійковій кодовій комбінації. Якщо кількість одиниць в двійковому коді парна, то контрольний символ дорівнює «0», якщо непарна - «1».

Таким чином у всіх кодових комбінаціях коду з перевіркою на парність кількість одиниць завжди повинна бути парною. Виявити спотворену внаслідок завад комбінацію можна на основі аналізу парності кількості одиниць в комбінації. Якщо парність порушена, кодова комбінація не приймається.

Схема кодера коду з перевіркою на парність залежить від того, як вводиться звичайний двійковий код – паралельно чи послідовно. На рис. 5.3 наведена схема кодера при паралельному введенні двійкового коду в регістр.

При подачі сигналу з рівнем логічної «1» на вхід L регістра, двійкова комбінація, яка подається на інформаційні входи D регістра DD1, записується на виходи Q1-Q4. Елементом, який виробляє п'ятий контрольний символ, є суматор за модулем 2 m2 - DD2.

Рисунок 5.3 – Кодер коду з перевіркою на парність при паралельному введенні в регістр двійкової кодової комбінації

Якщо кількість одиниць на його вході парна, то на його виході з'явиться нуль, якщо непарна – одиниця. Тому в деяких літературних джерелах суматор за модулем два називається генератором парності.

Таким чином, вхідна чотирирозрядна комбінація на вході кодера автоматично перетворилась в п'ятирозрядну. П'ятий символ – контрольний, який в приймальному пристрої дозволяє визначити чи є помилка в прийнятій комбінації.

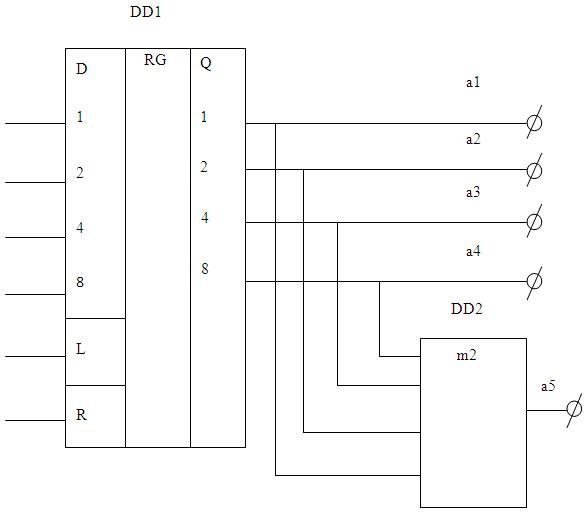

Якщо інформаційна комбінація звичайного двійкового коду вводиться в кодер послідовно, схема ускладнюється (рис. 5.4).

Рисунок 5.4 – Кодер коду з перевіркою на парність при послідовному введенні інформації в регістр

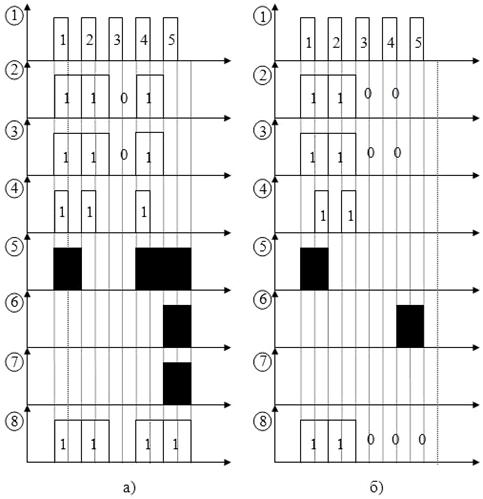

Для пояснення роботи схеми наведемо часові діаграми її роботи на прикладі чотирирозрядного двійкового коду 1101 i 1001 (рис. 5.5).

Вхідна інформаційна двійкова комбінація 1101 надходить на послідовний вхід послідовного регістра U2 i виводиться в послідовному коді через елемент U7 на зовнішні пристрої відповідно до тактових імпульсів генератора U1 (рис. 5.5, а). Елементом, що визначає парність одиниць вхідної комбінації, є лічильний тригер U5. При парній кількості імпульсів, що надходять на його лічильний вхід, на прямому виході тригера встановиться рівень логічного нуля, при непарній – рівень логічної одиниці. Якщо діє вхідна комбінація 1101, то протягом перших чотирьох тактів вона пройде на зовнішні пристрої. П'ятий імпульс від генератора виділяється з послідовності імпульсів схемою U3, яка є подільником частоти на 5. Цим імпульсом знімається інформація про стан прямого входу тригера U5, передається через елемент U7 і додається до основної кодової комбінації.

![]()

Рисунок 5.5 – Часові діаграми роботи кодера з перевіркою на паpнicть

при послідовному введенні інформації в peгістр

а) для комбінації 1101; б) для комбінації 1001

По суті лічильний тригер виконує таку ж функцю як суматор за модулем два в схемі рис. 5.3.

Елемент U4 розділяє інформаційні одиниці вхідного коду паузою, якщо вони слідують одна за одною.

Декодер коду з перевіркою на парність

Декодером коду з перевіркою на парність називається електронний пристрій, який аналізує прийняту комбінацію на парність i, якщо вона порушена, забороняє її подальше перетворення. Якщо прийнята комбінація записана в послідовно-паралельному peгістрі, то схема декодера має такий вигляд (рис. 5.6).

Рисунок 5.6 – Декодер коду з перевіркою на парність

Прийнята в послідовно-паралельний регістр комбінація коду з перевіркою на парність, надходить на суматор за модулем 2 DD2, аналізується, i в разі, якщо кількість одиниць парна, на інверсному виході суматора з'явиться piвень логічної одиниці, який поступає на всі елементи схеми DD3.

При наявності роздільного імпульсу, який надходить одночасно на всі елементи схеми DD3, прийнята комбінація з'являється на виходах Q1 - Q4 i проходить далі. Якщо парність порушена, на виході інверсного суматора за модулем два m2 з'явиться рівень логічного нуля, який закриє вci елементи DD3 i прийнята комбінація далі не пройде.

5.4.2 Код з прямим повторенням

Існує ряд кодів, в яких для збільшення завадозахищенності до інформаційної кодової комбінації, яка складається з n0 інформаційних символів двійкового безнадлишкового коду, додається k контрольних символів, причому k = п0. Таким чином загальна кількість елементів в кодовій комбінації дорівнює 2п0. Тому такі коди називають кодами з подвоєнням числа елементів.

В залежності від способу утворення контрольних символів такі коди класифікують на:

а) коди з прямим подвоєнням;

б) коди з інверсним подвоєнням;

в) кореляційні коди.

Розглянемо більш детально схеми, що реалізовують вказані вище коди.

Кодер коду з прямим повторенням

Кодер коду з прямим повторенням - це пристрій, який автоматично добавляє до інформаційної кодової комбінації двійкового коду таку ж саму (повторює її), збільшуючи загальну кількість двійкових символів вдвічі.

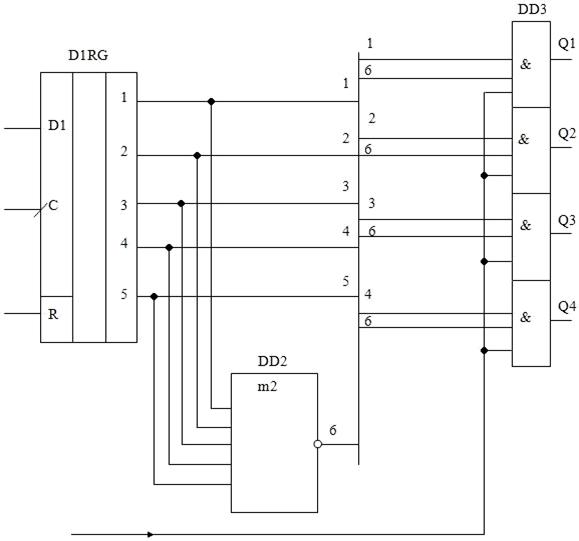

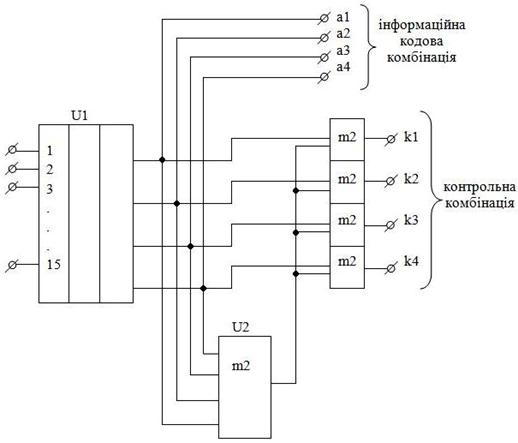

На рис. 5.7 зображена схема такого кодера. Припустимо, що кількість інформаційних символів двійкового коду n0=4.

Рисунок 5.7 – Кодер коду з прямим повторенням

Вхідний код передається на входи D1-D4 мультиплексора U3. П’ятий - восьмий входи цього ж мультиплексора паралельно з'єднуються відповідно з першим - четвертим його входами. При надходженні імпульсів від генератора U1 на вхід двійкового лічильника U2 на його виходах утворюється двійковий (адресний код), який управляє перетворенням паралельного коду на входах мультиплексора у послідовний на його виході. Таким чином, якщо на входах мультиплексора подано код 1101, то за 8 тактів генератора на подальше перетворення зовнішніми пристроями надійде код 11011101.

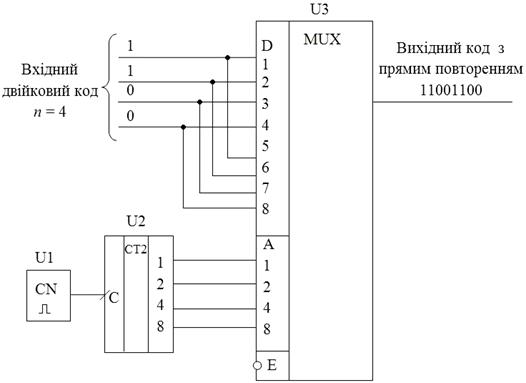

Декодер коду з прямим повторенням

Декодер коду з прямим повторенням (рис. 5.8) порівнює інформаційні та контрольні символи комбінації, що надійшли на приймач (вони повинні повторювати одна одну) i дає команду на її подальше перетворення, якщо дія завади не виявлена.

Рисунок 5.8 – Декодер коду з перевіркою з прямим повторенням

Після запису в послідовно-паралельний peгicтр U1 комбінація коду з прямим повторенням з'явиться на виходах 1-8 регістра. Комбінації на виходах 1-4 i 5-8 повторюють одна одну. Відповідні символи комбінацій п0 (на виходах 1-4 регістра) порівнюються із символами k = n0 (на виходах 5-8) за допомогою блока суматорів за модулем 2 – U3.

Якщо комбінація коду з прямим повторенням прийнята правильно на виходах вcix суматорів за модулем 2 буде рівень логічного нуля. На виході схеми «АБО» U4 також буде рівень логічного «0» i тригер U5 знаходиться у початковому стані (прямий вихід тригера має потенціал логічного «0». На виходах блока елементів U6 також зберігається рівень логічного «0», бо вони закриті нульовим потенціалом входу, який дозволяє зчитування інформації EWR. Імпульс на цьому вході з'являється після закінчення записування вciєї комбінації в регістр. Якщо комбінація коду має п розрядів, то роздільний імпульс з'являється на п+1 такті (в нашому прикладі на дев'ятому такті).

В момент надходження цього імпульсу логічні елементи блока U6 відкриваються, на вході нижнього елемента цього блока з'являється рівень логічної одиниці, який відкриває вci елементи «I» блока U2. Вихідна комбінація D1-D4 з виходів регістра 1-4 через елементи «I» блока U2 подається для подальшого перетворення.

Якщо внаслідок дії завад комбінація буде спотворена, на одному (чи декількох) виходах суматорів блока U3 з'явиться рівень логічної одиниці, який приведе тригер U5 в одиничний стан. 9-й тактовий імпульс на вході EWR відкриває верхній логічний елемент блока U6, на його виході з'явиться рівень логічної одиниці, який надійде на входи R регістра Ul i тригера U5 i скине їх у початковий стан (комбінація стирається). Елементи блока U2 при цьому будуть закриті i спотворена завадами комбінація на його виходах не з'явиться.

Звернемо увагу на те, що вихідний блок декодера U2 містить тільки чотири інформаційні розряди. Контрольні розряди виконали свою роль при аналізі правильності прийнятої комбінації i в подальшому не використовуються.

5.4.3 Коди з інверсним повторенням (iнверсні коди)

Коди з інверсним повторенням інформаційної двійкової кодової комбінації утворюються за таким правилом: якщо кількість одиниць в інформаційній комбінації парна, то до неї автоматично додається така сама комбінація (пряме повторення) i якщо кількість одиниць в інформаційній комбінації непарна, до неї додається інвертована інформаційна комбінація. Наприклад, якщо інформаційна кодова комбінація має вигляд 1100, то до неї додається така сама комбінація 1100 i в цілому для подальшого перетворення надійде комбінація 11001100.

Якщо інформаційна комбінація має вигляд 1110, то до неї буде додана комбінація 0001 i комбінація інверсного коду буде мати вигляд 11100001.

Кодер коду з інверсним повторенням

Кодером коду з інверсним повторенням називається електронний пристрій, який до інформаційної n0-розрядної комбінації двійкового коду автоматично додає контрольну комбінацію з k=n0 символів за таким алгоритмом: якщо кількість одиниць інформаційного коду парна, то до неї додається така ж сама комбінація, якщо непарна, до неї додається інвертована інформаційна комбінація. Схема такого кодера наведена на рис. 5.9.

Рисунок 5.9 – Схема коду з інверсним повторенням

Інформаційна кодова комбінація з'являється на виходах кодера U1 при подачі на один з його 16 входів рівня логічної «1». Суматор за модулем 2 U2 аналізує парність кількості одиниць в інформаційній кодовій комбінації.

Якщо ця кількість парна, на його виході з'явиться рівень логічного нуля i на виходи блока суматорів за модулем 2 U3 пройдуть вci символи, які встановились на виходах кодера U1. Якщо кількість одиниць інформаційної комбінації непарна, на виході елемента U2 з'явиться рівень логічної одиниці i на виходи блока U3 пройдуть інвертовані символи інформаційної кодової комбінації, яка встановилась на виходах кодера U1, тобто схема працює за встановленим алгоритмом.

Декодер коду з інверсним повторенням

Декодер коду з інверсним повторенням – пристрій, який за відомим алгоритмом утворення порівнює інформаційні та контрольні символи, що надійшли на приймальний пристрій, i дає команду на її подальше перетворення, якщо дія завади не виявлена.

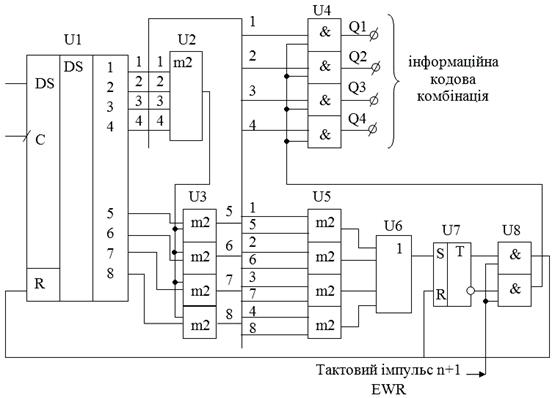

Схема декодера інверсного коду подана на рис.5.10.

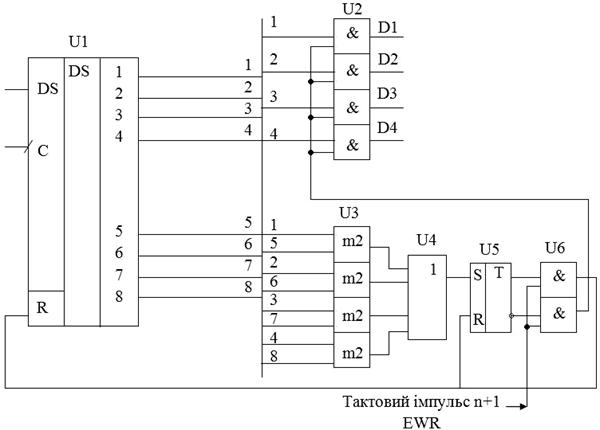

Рисунок 5.10 – Декодер інверсного коду

Декодер працює таким чином. Прийнята комбінація надходить на вхід DS послідовно-паралельного регістра U1 i після надходження на вхід «С» п тактів фіксується на виходах 1-8 регістра. (На виходах 1-4 – інформаційна частина кодової комбінації, на виходах 5-8 - контрольна комбінація).

Суматор за модулем 2 U2 аналізує кількість одиниць в інформаційні частині кодової комбнації i дає команду на інвертувальний блок U3, в залежності від парності кількості одиниць в інформаційній комбінації, символи контрольної комбінації на виходах 5-8.

В результаті при правильному надходженні комбінації інверсного коду інформаційна комбінація з виходів регістра 1-4 i комбінація з виходів блока U3 повинні бути однаковими. Блок суматорів за модулем 2 U5 порівнює відповідні символи цих комбінацій i при правильному прийомі на виходах повинні бути рівні логічного «0». При наявності помилки в прийнятій комбінації на одному (чи декількох) виходах блока U5 з'явиться логічна «1», тригер U7 перейде в одиничний стан i після надходження на вхід EWR п+1 тактового імпульсу через верхній логічний елемент блока U8 скидає (стирає) дані, які були записані в регістр Ul; i повертає тригер U7 в початковий стан. При правильному прийомі після надходження на вхід EWR п+1 імпульсу (в нашому прикладі – 9-го) сигнал з нижнього елемента «I» блока U8 дає дозвіл на проходження інформаційної частини кодової комбінації інверсного коду через елементи «I» блока U4 для подальшого перетворення.

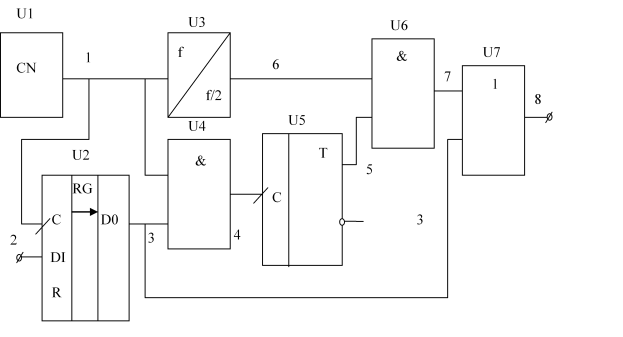

5.4.4 Кореляційний код

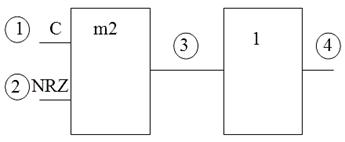

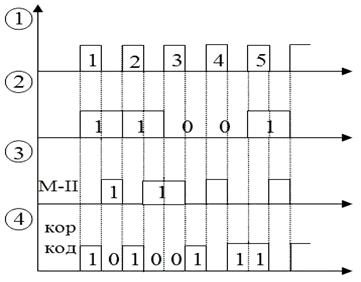

Кодером кореляційного коду є електронний пристрій, який при надходженні на його входи n0 інформаційних символів двійкового коду автоматично додає до кожного інформаційного символу по одному контрольному "0" чи "1" i значення якого утворюється за правилом: інформаційний нуль перетворюється в 01, інформаційна одиниця перетворюється в 10. Таким чином загальна кількість символів кодової комбінації кореляційного коду п = n0 +k = 2n0. Тому цей код відносять до коду з подвоєнням числа елементів. Схема кодера кореляційного коду наведена на рис. 5.11, а часові діаграми його роботи на рис. 5.12.

Рисунок 5.11 – Кодер кореляційного коду

Рисунок 5.12 – Часові діаграми роботи кодера кореляційного коду

Декодер кореляційного коду

Декодером кореляційного коду є пристрій, який аналізує прийняту кодову комбінацію. На прийомі помилка визначається в тому випадку, коли в парних елементах містяться однакові символи, тобто 11 чи 00 (заміcть 10 та 01). При правильному прийомі парні елементи відкидаються i залишається початкова комбінація.

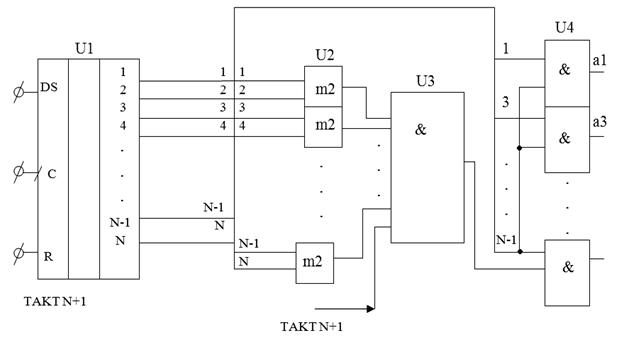

Схема декодера кореляційного коду наведена на рис. 5.13.

Для виявлення помилки прийнята кодова комбінація розбивається на групи по 2 символи в кожній i аналізується парність кожної групи.

В разі правильного прийому в кожній групі мають бути pізні символи (01 чи 10). Якщо в будь-якій групі прийняті однакові символи (00 чи 11) – комбінація вважається спотвореною завадами i стирається, тому що в такому випадку помилка не виявляється.

Означений алгоритм виявлення помилки реалізовується таким чином.

Протягом N в послідовно-паралельний регістр U1 записується комбінація прийнятого кореляційного коду. Кожна пара символів (1-2, 3-4,... , [(N-1)- N]) порівнюється за допомогою суматорів за модулем 2 (блок U2) i в paзi правильного прийому на вcix виходах суматорів будуть piвнi логічної "1", які надходять на входи схеми "I" U3. 3 надходженням (N +1) тактового імпульсу від схеми управління на виході елемента U3 виникне імпульс, який дасть дозвіл на подальше перетворення інформаційної частини комбінації (символи Ul, U3, U5,..... UN-1).

Рисунок 5.13 – Декодер кореляційного коду

В разі наявної помилки в будь-якій парі символів на виході елемента U3 значення логічного "0" не змінюється з приходом (N+l)-го такту i комбінація через блок елементів U4 не пройде.

3 приходом (N+2) такту записана в регістр U1 комбнація кореляційного коду скидається.

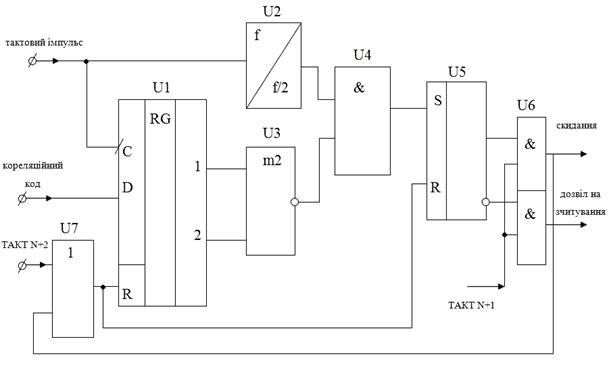

На рис. 5.14 подана ще одна схема декодера кореляційного коду.

В цій cxeмi кожна пара символів кореляційного коду порівнюється між собою одним суматором за модулем 2 безпосередньо під час послідовного надходження символів коду на вхід послідовно-паралельного регістра U1, який має тільки два виходи. Елемент U3 -суматор за модулем 2 з інверсією порівнює кожну пару символів через кожних 2 такти.

Рисунок 5.14 – Схема декодера кореляційного коду

Для того, щоб результат порівняння кожної пари символів здійснювався тільки на парних тактах вхідних імпульсів, дозвіл на передачу результату порівняння подається через подільник частоти тактових імпульсів U2 з коефіцієнтом підрахунку 2. В разі, коли у відповідний пapi символів з'являться однакові символи, на виході елемента U3 з'явиться рівень логічної "1", який буде записаний в RS-тригер U5. Після закінчення прийому кодової комбінації кореляційного коду на (N +1) такті елементи схеми U6 дають дозвіл на зчитування інформації в разі правильного прийому або на скидання інформації при наявності помилки. 3 надходженням (N+2) такту регістр Ul i тригер U5 скидаються в обох випадках i починається аналіз нової кодової комбінації.